配屏是日常工作中不可避免的,往往同一颗chip不同的机型最大的区别就是屏幕不一样,目前比较常遇到的就是Tcon和LVDS屏,下面将对LVDS屏幕进行简单介绍。

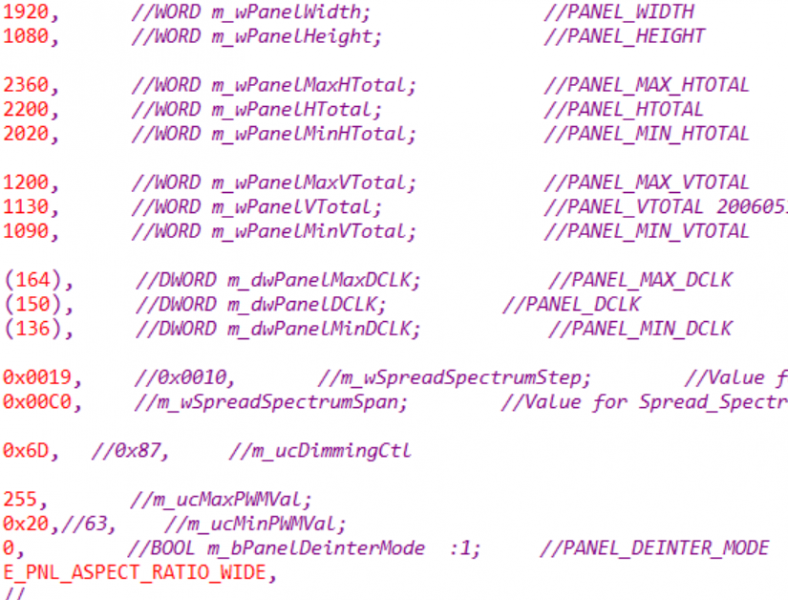

根据Panel Spec 配置好屏参,填到的屏参数table表里面,添加时可以选择类似分辨率的,拷贝一份,然后根据spec的的具体值去设置。

下面简单介绍下关键的参数配置。

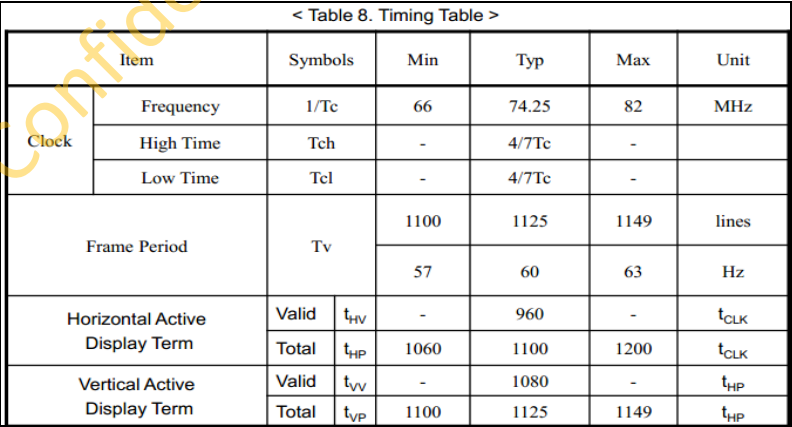

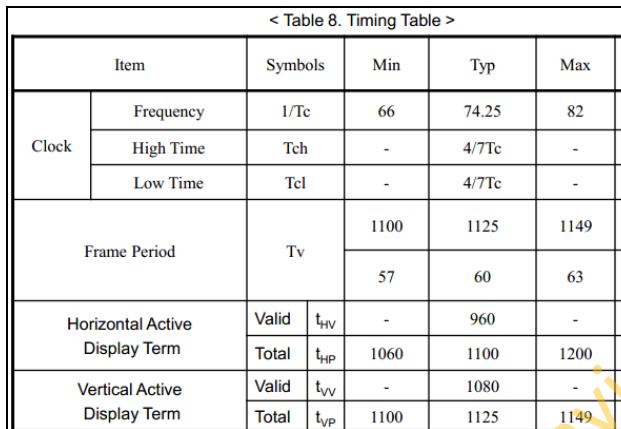

1.按照Timing Table配置 TOTAL,DCLK值:

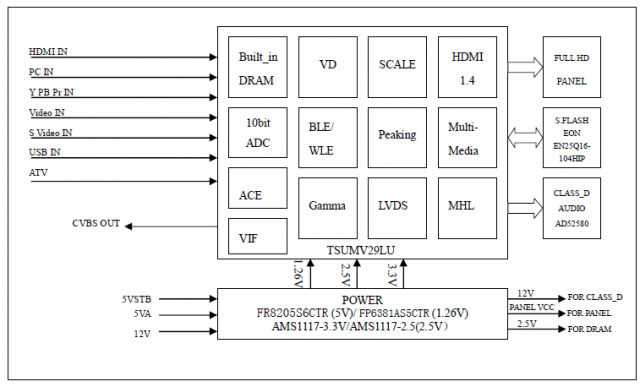

正常的流程是SOC给出LVDS信号或者VB1信号给TCON,TCON出miniLVDS信号或者EPI等给到屏幕,我们平时看到屏幕参数都是TCON对SOC的要求,并非屏幕对TCON的要求

2.panel max/min值设置

pll setting 就是BK1031_1E/1F/20(8bit address)的设定值

PLL MAX/MIN SET算法:

Dclk = XTAL*MM*824288*LM*K/(SET*A),其中

i. Dclk = Htt*Vtt*FR

ii.XTAL 为系统所使用的振荡器频率,通常为12MHZ

iii.MM*XTAL/MHZ 必须等于 216 所以 MM= 216/12 =18

iv.LM建议值为 8

v.K建议值为1

vi.A: LVDS dual channel 时为3.5,single Channel 的话为7

这个算出来只是理论值,之后哟啊根据实际情况是微调。如果panel没有锁住,MM下播放视频滚动,可以适当放大 min 和 Max的范围调整

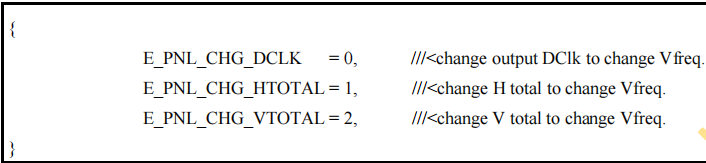

3. panel m_ucOutTimingMode设置

code里面有三种模式设置,如下:

非TCON屏幕:

首选E_PNL_CHG_VTOTAL,其次是E_PNL_CHG_DCLK,E_PNL_CHG_HOTAL使用的比较少。具体要针对panel的spec来设置。

TCON屏:

首先E_PNL_CHG_LOCK,因为控制TCON屏的TCON控制信号宽度,位置的Value都是参考VTOTAL来设定的,VTotal变化TCON波形就会变化。另外如果选择E_PNL_CHG_VOTAL那么在50/60HZ切换的时候,由于VTOTAL的变动经常会有屏幕上下抖动一下或者几下的问题。

但是屏幕方面很明确要稳定DCLK,这个时候我们就必须选择E_PNL_CHG_VTOTAL

当然,也许有些情况 使用E_PNL_CHG_DCLK也不适用,那就要具体问题具体分析看了。E_PNL_CHG_HTOTAL使用较少,但是这个要根据实际的SPEC来区分

看如下SPEK截图,可以看到VTOTAL值很窄(1100-1149),这样如果选择E_PNL_CHG_VTOTAL模式,很有可能由于VOTAL太窄,就会辺在50/60HZ切换屏幕时闪烁,MM下播放VIDEO无法LOCK等情况,所以这个屏幕我们会选择用E_PNL_CHG_DCLK。

闪烁的原因:是当从50HZ到60HZ切换的时候,在Frame进行锁定的过程中,总会改变到VTOTAL的值,而且这个值变化量又比较大,如果屏幕容忍一次的该变量不够,就会出现闪烁。因为是在lock过程中出现,所以软件用Frame Free run的方式去规避没有作用。

4:确认屏幕是否 lock

以上步骤完成以后,一定要确认50/60HZ下以及互补切换时候,panel是否可以正常lock,可以在50/60HZ下分别读取寄存器:0x1031有54的值是否有01F4(55为01),如果是,就表示锁定到了。

常用的寄存器有下面几个

当碰到点屏幕不亮,或者颜色异常的时候,可以试试敲这几个寄存器

REG_3294_BIT0(PANLE_SWAP_PORT)

REG_3294_BIT1(PANLE_DUAL_PORT)

REG_3294_BIT2(PANLE_INV_DE)

REG_3294_BIT3(PANLE_INV_VSYNC)

REG_3294_BIT4(PANLE_INV_DCLK)

REG_3280_BIT2?PANEL_LVDS_TI_MODE

REG_3280_BIT5?PANEL_LVDS_LVDS_POL

REG_3280_BIT6?PANEL_LVDS_LVDS_CH

本网站为Mstar的爱好者建立,以上所有可提供资料与技术支持,QQ 921685776 zgtech@qq.com

液晶发烧友

液晶发烧友